日本DNP实现2nm工艺光掩模图案化 迈向更精细芯片制造

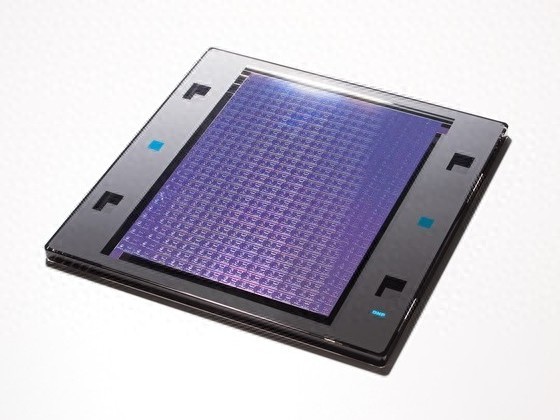

DNP大日本印刷本月12日宣布,成功在其光掩模制品上绘制了支持2nm及以下EUV工艺的精细光掩模图案。该企业还完成了支持High NA EUV光刻的光掩模的初步评估,并已向生态合作伙伴出样。

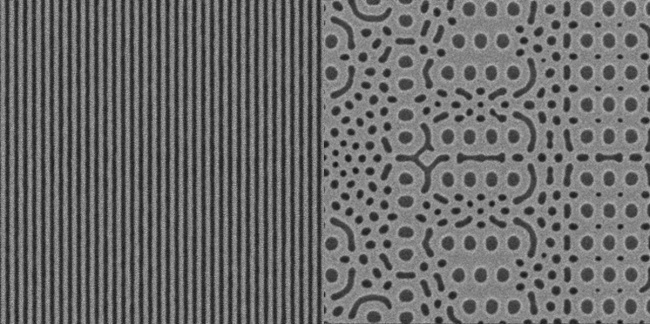

在现代光刻系统中,光掩模上的“大图案”是晶圆上芯片电路“小图案”的模板。DNP在2023年完成了适用于3nm工艺的光掩模开发。满足2nm及以下工艺的光掩模不仅需要在直线图案尺寸上较3nm世代产品缩小20%,还需要在复杂度更高的曲线图案上实现同比例的尺寸压缩。

DNP此次成功绘制精细图案,意味着其光掩模产品可满足2nm及以下名义制程逻辑半导体的生产需求,为更高效逻辑芯片的曝光打下了基础。DNP计划于2027财年(起始于同自然年4月)实现2nm光掩模量产。

考虑到DNP和Rapidus的合作关系,DNP的新光掩模预计将用于Rapidus计划于2025年4月启动的2nm试产线。

免责声明:本文章由会员“极目新闻”发布如果文章侵权,请联系我们处理,本站仅提供信息存储空间服务如因作品内容、版权和其他问题请于本站联系